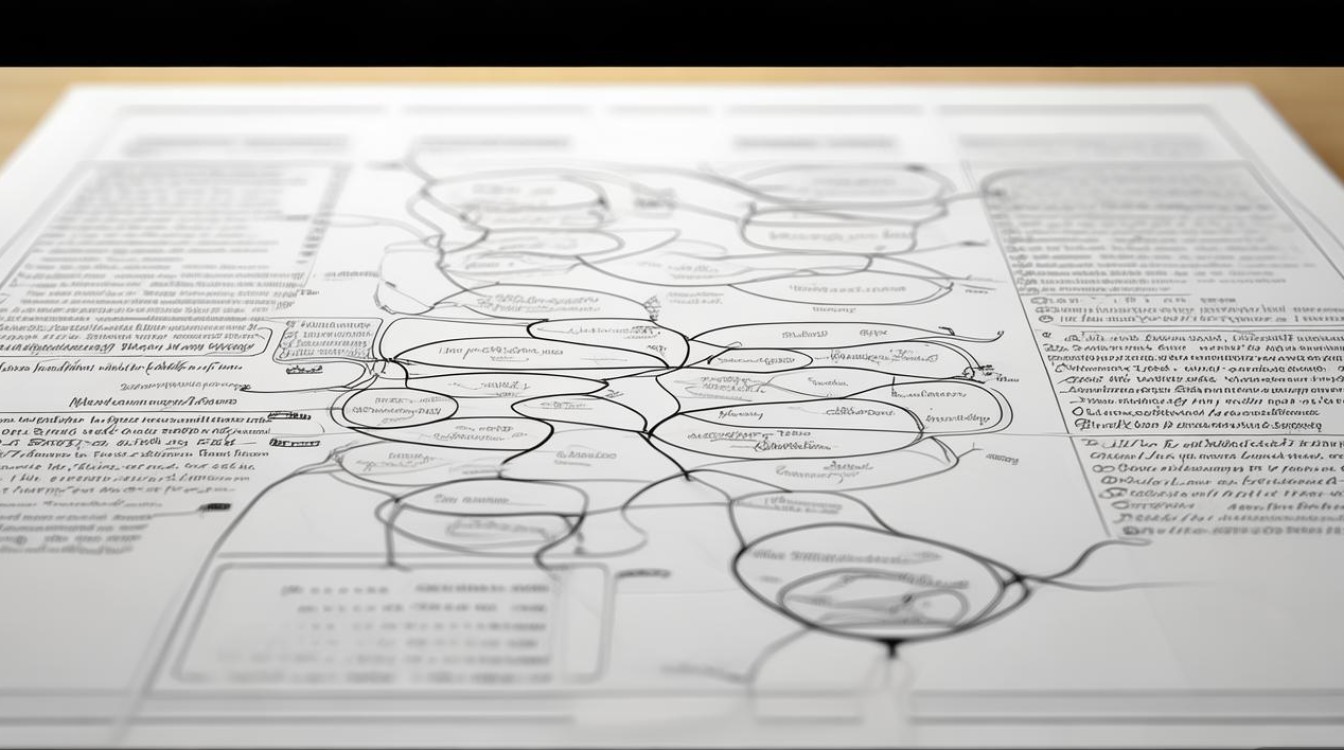

计算机组成原理 思维导图

中心主题:计算机组成原理

计算机系统概述

- 1 基本概念

- 冯·诺依曼体系结构

- 五大部件:运算器、控制器、存储器、输入设备、输出设备

- 核心思想:存储程序、顺序执行

- 计算机的层次结构

- 微程序级 / 逻辑门级

- 微体系结构级 (本课程核心)

- 指令系统级

- 操作系统级

- 汇编语言级

- 高级语言级

- 应用语言级

- 冯·诺依曼体系结构

- 2 性能指标

- 基本性能

- 吞吐量:单位时间内处理的信息量

- 响应时间:从开始到结束的时间

- CPU时钟周期:时钟频率的倒数

- CPU性能

- CPI (Cycles Per Instruction):执行一条指令所需的平均时钟周期数

- IPS (Instructions Per Second):每秒执行百万条指令数

- FLOPS (Floating-point Operations Per Second):每秒执行浮点运算次数

- 性能公式

CPU执行时间 = (指令条数 × CPI) / 主频CPU执行时间 = CPI × CPI / 主频MIPS = 主频 / (CPI × 10⁶)

- 基本性能

数据的表示与运算

- 1 数值数据的表示

- 进位制

二进制、八进制、十六进制、十进制及其转换

- 定点数与浮点数

- 定点数

- 纯整数:符号位 | 数值位

- 纯小数:符号位 | 数值位

- 表示范围有限

- 浮点数 (IEEE 754标准)

- 格式:

符号位(S) | 阶码(E) | 尾数(M) - 规格化:

M的最高位为1 (或隐含1) - 特殊值:无穷大、非数、0

- 格式:

- 定点数

- 进位制

- 2 非数值数据的表示

- 字符编码

- ASCII码

- Unicode / UTF-8

- 图像编码

像素、位图、矢量图

- 字符编码

- 3 数据校验

- 奇偶校验码:简单,检错,无法纠错

- CRC循环冗余校验码:检错能力强

- 海明码:既能检错又能纠错

- 4 算术逻辑运算

- 定点数加减运算

- 补码加减法:

[A+B]补 = [A]补 + [B]补 - 溢出判断:双符号位法 / 单符号位进位判断法

- 补码加减法:

- 定点数乘除运算

- 原码乘除法 (符号位与数值位分开运算)

- 补码乘除法 (Booth算法)

- 浮点数运算

- 对阶:小阶向大阶看齐

- 尾数相加/减

- 规格化

- 舍入

- 判溢出:阶码溢出

- 定点数加减运算

存储系统

- 1 存储器层次结构

- 目的:解决速度、成本、容量之间的矛盾

- Cache-主存-辅存 三级结构

- 程序访问的局部性原理

- 时间局部性

- 空间局部性

- 2 主存储器

- 基本组成:存储体、地址寄存器、数据寄存器、读写控制电路

- 随机存取存储器

- SRAM (静态RAM):速度快,不需要刷新,用于Cache

- DRAM (动态RAM):集成度高,需要刷新,用于主存

- 只读存储器

- MROM, PROM, EPROM, EEPROM, Flash Memory

- 主存与CPU的连接

- 地址线:选择存储单元

- 数据线:传输数据

- 控制线:读/写控制

- 主存扩展

- 位扩展:增加存储字长

- 字扩展:增加存储单元数量

- 3 高速缓存

- 工作原理:基于局部性原理,用速度快但容量小的Cache存放主存中活跃数据的副本

- 地址映射

- 直接映射:简单,冲突率高

- 全相联映射:灵活,比较器复杂

- 组相联映射:折中方案

- 替换算法

- LRU (最近最少使用):性能好,实现复杂

- FIFO (先进先出):实现简单,性能一般

- 随机替换

- 写策略

- 写直达:同时写入Cache和主存,简单但慢

- 写回:只写Cache,替换时写回主存,快但复杂

- 4 辅助存储器

- 硬盘

- 结构:盘片、磁头、主轴电机

- 性能指标:平均寻道时间、平均旋转延迟、数据传输率

- 固态硬盘

- 优点:速度快、抗震、低功耗

- 原理:基于闪存

- 硬盘

指令系统

- 1 指令格式

- 操作码:指出指令的功能

- 地址码:指出操作数的地址或结果地址

- 指令字长度:一个指令占用的位数

- 寻址方式:如何找到操作数

- 2 寻址方式

- 立即寻址:操作数在指令中

- 直接寻址:操作数地址在指令中

- 间接寻址:指令给出的是操作数地址的地址

- 寄存器寻址:操作数在寄存器中

- 寄存器间接寻址:寄存器中存放的是操作数地址

- 相对寻址:

PC + A,用于转移指令 - 基址寻址:

BR + A,用于程序重定位 - 变址寻址:

IX + A,用于处理数组

- 3 指令类型

- 数据传送类:

MOV,PUSH,POP - 算术逻辑运算类:

ADD,SUB,AND,OR - 程序控制类:

JMP(无条件跳转),JZ(结果为0跳转),CALL(子程序调用),RET(返回) - 输入/输出类:

IN,OUT

- 数据传送类:

中央处理器

- 1 CPU的功能和基本结构

- 功能:指令控制、操作控制、时间控制、数据加工

- 基本组成

- 运算器:ALU (算术逻辑单元),通用寄存器,状态寄存器

- 控制器:指令控制单元,时序发生器

- 2 数据通路

- 概念:数据在CPU内部各部件之间流动的路径

- 总线结构:单总线、多总线

- 3 指令周期

- 取指周期:从内存中取出指令

- 间址周期:获取有效地址

- 执行周期:执行指令功能

- 中断周期:处理中断

- 4 控制方式

- 硬布线控制器:使用组合逻辑电路,速度快,设计复杂

- 微程序控制器

- 思想:将每条机器指令的控制信号序列编写成一个“微程序”

- 组成:控制存储器、微指令寄存器、微指令地址寄存器

- 优点:设计规整、易于修改和扩展

- 缺点:比硬布线慢

- 5 数据通路与控制器设计

- 组合逻辑 (硬布线) 设计方法

- 微程序设计方法

总线系统

- 1 总线的基本概念

- 定义:连接多个部件的一组共享通信线路

- 分类

- 按功能:数据总线、地址总线、控制总线

- 按连接部件:片内总线、系统总线、通信总线

- 2 总线仲裁

- 集中式仲裁

- 链式查询:结构简单,优先级固定

- 计数器定时查询:优先级可以改变

- 独立请求:响应速度快,控制线多

- 分布式仲裁

- 集中式仲裁

- 3 总线定时

- 同步定时:由统一的时钟信号控制,简单但不灵活

- 异步定时:采用“请求-应答”方式,灵活但复杂

- 4 总线标准

- 系统总线:PCI, PCI Express

- 外设总线:USB, SATA, HDMI

输入/输出 系统

- 1 I/O接口

- 功能:数据缓冲、格式转换、设备选择、状态检测

- I/O端口编址

- 统一编址:I/O端口与内存单元统一地址空间

- 独立编址:I/O端口有独立的地址空间

- 2 I/O方式

- 程序查询方式:CPU主动查询I/O状态,效率低

- 中断方式:I/O完成后主动通知CPU,解放CPU

- DMA方式 (直接存储器存取)

- 核心思想:数据传输由DMA控制器完成,CPU只在传输开始和结束时介入

- 优点:传输速度快,CPU负担小

- 传送过程:请求、响应、传输、结束

- IO通道方式:更高级的DMA,可以执行简单的通道程序

其他

- 流水线技术

- 思想:指令的取指、译码、执行等步骤并行化

- 吞吐率:单位时间内完成的指令数

- 加速比:不使用流水线的执行时间 / 使用流水线的执行时间

- 流水线冲突:结构冲突、数据冲突、控制冲突

- RISC与CISC

- CISC (复杂指令集计算机):指令数量多,功能复杂,周期不固定

- RISC (精简指令集计算机):指令数量少,格式规整,单周期执行,大量寄存器

总结与关联

这个思维导图展示了计算机组成原理的完整知识体系,学习时,应重点关注数据通路和控制信号这两条主线,理解CPU是如何在时钟的驱动下,通过总线与存储器和I/O设备协同工作,最终执行指令系统中的指令来完成任务的,理解了这些核心部件如何交互,就掌握了计算机组成的精髓。